1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. Switch SPDT

2. Logic Probe

Logic probe adalah alat yang dapat menganalisa suatu

rangkaian IC dengan cara menunjukkan logika keluaran dari kaki pin IC tersebut

.

3. J-K Flip-Flop

(74LS112)

JK flip-flop digunakan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). Counter (rangkaian logika sekuensial yang dibentuk dari flip-flop.

Pada percobaan 1 ini dirangkai suatu rangkaian Shift Register (register geser) keluaran output 4 bit . Pada rangkaian shift register keluaran 4 bit ini berarti menggunakan 4 buah IC J-K flip flop sebagai perwakilan 1 bit keluaran untuk 1 buah J-K flipflop.

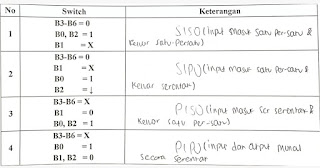

Pada rangkaian ini memiiki 4 input masukan dari J-K flip flop dan 4 input keluaran dari J-K flip flop dimana akan terjadi proses operasi SISO, SIPO, PISO, dan PIPO pada rangkaian sesuai pengaturan switch dan kondisi.Maka padaprosesnya akan terjadi sistem kerja serial dan paralel yang dimana pada rangkaian akan terjadi perwakilan dari penggeseran pada sistem serial maupun serempak pada sistem paralel baik itu masukan maupun keluaran suatu biner yang dimana pergeseran maupun serempak pada sistem serial dan paralel ini akan mewakili MSB dan LSB dari 4 bit binner masukan dan keluaran. Terjadinyam proses input dan output logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Analisa output yang dihasilkan tiap kondisi

-Kondisi pertama, B3-B6 dinolkan, B0 &B2 =1, dan B1 berperan sebagai input, diambil contoh memasukkan bil biner 0011 maka diatur di switch B1 dan terlihat pada output, keluarannya muncul satu per-satu maka hal ini sesuai dengan pengertian jenis shift register SISO (Serial In Serial Out).

- Kondisi kedua, B3-B6=0 sebagai input, B1 sebagai input, B0=1,B2 fall time. Dimasukkan input 0011 pada switch B1, terlihat pada output keluarannya muncul serentak hal ini sesuai dengan definisi SIPO (Serial in Serial Out) dimana jalur input 1 dan output sesuai dengan flip-flop yang digunakan

- Kondisi ketiga, B3-B6 sebagai input, B0=1, B1 & B2 = 0 dimasukkan input 0011 pada switch B3-B6 terlihat bahwa jalur input sebanyak flip flop yang digunakan dan output keluaran muncul satu per-satu maka hal ini sesuai dengan definisi Paralel In Serial Out(PISO)

- Kondisi keempat , B3-B6 sebagai input , B0 =1, B1&B2 dimasukan input 0011 dan terlihat pada output muncul serentak maka hal ini sesuai dengan Paralel in Paralel Out (PIPO)

2. Jika gerbang and pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip-flop, dibandingkan output yang didapatkan

- Pada saat sumber clock langsung dihubungkan hal yang terjadi adalah pada flip-flop kedua error dan tidak mengeluarkan output.

7. Link Download

[Kembali]

.png)

Tidak ada komentar:

Posting Komentar