1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. Switch SPDT

2. Logic Probe

Logic probe adalah alat yang dapat menganalisa suatu

rangkaian IC dengan cara menunjukkan logika keluaran dari kaki pin IC tersebut

.

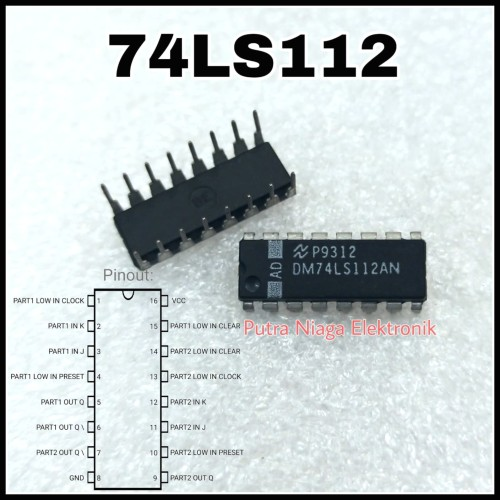

3. J-K Flip-Flop

(74LS112)

JK flip-flop digunakan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). Counter (rangkaian logika sekuensial yang dibentuk dari flip-flop.

Pada rangkaian ini menggunakan 4 buah RS flip-flop sehingga outputnya menjadi 4 bit. Dengan dua buah switch SPDT yang terhubung ke sumber Vcc. Pada flip flop pertama input clocknya terhubung dengan komponen clock lalu outputnya berupa logic probe yang terhubung pada kaki output q pada flip flop, sehingga disebut dengan counter up dimana rangkaian counter ini akan menghitung bilangan desimal dari terendah sampai desimal tertinggi. Bilangan desimal ini didapat dari jumlah kombinasi bilangan biner dari rumus 2^n-1 dengan n adalah jumlah bit sehingga jumlah kombinasinya adalah 15.

Jika output logic probe terhubung ke kaki output Q bar maka disebut dengan counter down dimana counter akan menghitung bilangan desimal dari tertinggi sampai desimal terendah. Pada flip flop selanjutnya kaki input clocknya dihubungkan pada output flip flop sebelumnya, dan begitu seterusnya. Sehingga, rangkaian ini disebut dengan Asynchronous Counter dimana outputnya akan menampilkan bilangan yang acak atau tidak berurutan

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Anaisa output berdasarkan ic yang digunakan?

→ Berdasarkan Percobaan 1 yang menggunakan IC 74LS112, yaitu dimana hasil output menghitung dari 0 naik sampari 15 dimana menampilkan bilangan 0000 hingga 1111 Schingga rangkaian ini merupakan Counter up

2 Analisa output percobaan berdasarkan sinyal output JK flip flop kedua dan ketiga!

→ Pada JK flip flop nilai outputnya tergantung pada inputan yang diberikan, dimana percobaan ini JK flip flop kedua menerima input dari JK flip flop yang pertama begitu seterusnya. Output JK akan berubah ubab=h ketika clock aktif dan JK dalam kondisi toggle

JK kedua harus menunggu output dari JK flip flop pertama dan jk flip flop ketiga harus menungguu dari jk flip flop kedua hal inilah yang menyebabkan rangkaian disebut counter Asynchronous

7. Link Download

[Kembali]

.png)

.png)

Tidak ada komentar:

Posting Komentar