1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. Switch SPDT

2. Logic Probe

Logic probe adalah alat yang dapat menganalisa suatu

rangkaian IC dengan cara menunjukkan logika keluaran dari kaki pin IC tersebut

.

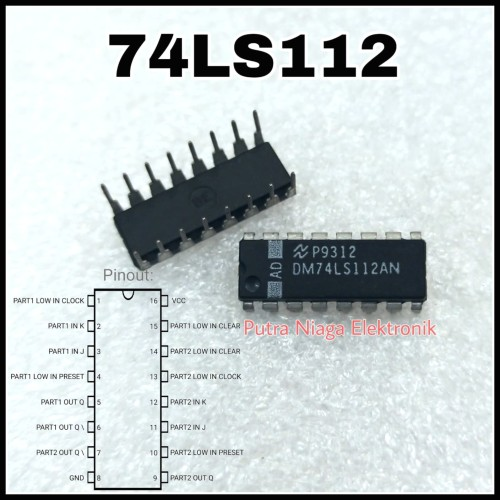

3. J-K Flip-Flop

(74LS112)

JK flip-flop digunakan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). Counter (rangkaian logika sekuensial yang dibentuk dari flip-flop.

Rangkaian ini merupakan rangkaian syncronus sehingga input untuk kedua ic nya di paralelkan sehingga kedua ic bisa bekerja dalam waktu yang bersamaan

pada kondisi ini dimana IC nya adalah 7493 dan 74LS190 hanya memiliki counter up sesuai dengan tabel kebenarannya

yaitu ketika semua kaki inputnya berlogika 1,perbedaan antara 74LS190 dan 74933 adalah pada maksimal penghitungannya

dimana pada 74LS190 maksimal countnya adalah 15 sedangkan pada 74933 maksimat countnya adalah 9.

kedua penghitungan ini dimulai dalam waktu yang sama karena berprinsip syncronus counter

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Analisa output percobaan berdasarkan IC yang digunakan

Berdasarkan output dari percobaan 2 terjadi counter up dikarenakan bilangannya naik dari 0 sampai 15 dan dari 0 sampai 9. Perbedaan jumlah bilangan maksimal counter ini disebabkan penggunaan IC yang berbeda yaitu 74LS190 dan 7493

2. Analisa hasil kondisi 3 pada percobaan 2a dengan kondisi 3 pada percobaan 2b

Pada percobaan 2a dan 2b kondisi 3 sama sama counter up tetapi terdapat sedikit perbedaan yaitu, pada 2a CLK B dihubungkan ke CLK A, sedangkan pada 2b CLK B dihubungkan ke Qa. Hal ini menyebabkan percobaan 2a counter up hanya pada Qb,Qc, dan Qd sedangkan pada percobaan 2b counter upnya dimulai dari Qa,Qb, dan Qd.

3. Apa pengaruh clock A dan clock B pada IC yang digunakan

CLK A dgiunakan sebagai input dari sinyal yang dimana untuk inputannya apabila tidak digunakan maka hanya mencacah sebanyak 3 bit yaitu 8 biner dan apabila digunakan maka CLK B harus disambung pada Qa yang kemudian dapat mencacah hingga 4 bit yaitu 16 biner.

7. Link Download

[Kembali]

.png)

.jpeg)

Tidak ada komentar:

Posting Komentar